### Features and Benefits

37.5MHz LVCMOS output

Operating temperature from -40°C to 125°C

3.3V supply voltage, 3.8mA typical current

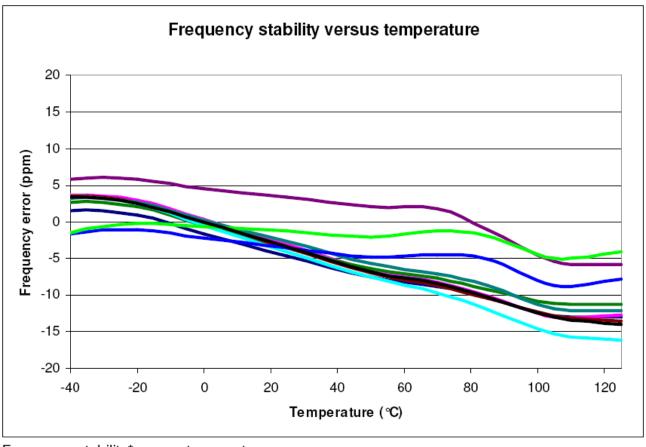

Excellent total frequency stability as low as ±20 ppm

RoHS and REACH compliant, Pb-free, Halogen-free and Antimony-free

# **Typical Applications**

Industrial, medical, non AEC-Q100 automotive, avionics and other high temperature applications Industrial sensors, PLC, motor servo, outdoor networking equipment, medical video cam, asset tracking systems, etc.

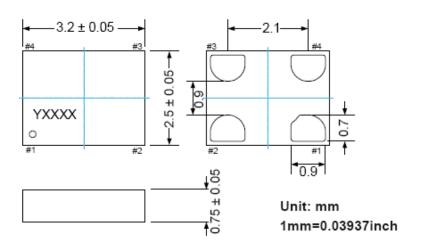

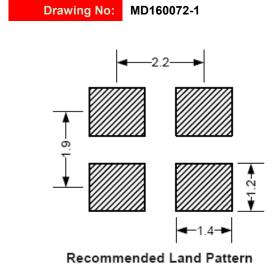

# Mechanical Drawing & Pin Connections

Table 1. Pin Description

| Pin | Symbol    |                  | Functionality                                                                                                                                      |

|-----|-----------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|     |           | Output<br>Enable | H <sup>[1]</sup> : specified frequency output<br>L: output is high impedance. Only output driver is disabled.                                      |

| 1   | OE/ ST/NC | Standby          | H <sup>[1]</sup> : specified frequency output<br>L: output is low (weak pull down). Device goes to sleep mode. Supply<br>current reduces to I_std. |

|     |           | No Connect       | Any voltage between 0 and Vdd or Open <sup>[1]</sup> : Specified frequency output. Pin 1 has no function.                                          |

| 2   | GND       | Power            | Electrical ground                                                                                                                                  |

| 3   | OUT       | Output           | Oscillator output                                                                                                                                  |

| 4   | VDD       | Power            | Power supply voltage <sup>[2]</sup>                                                                                                                |

## Notes:

- 1. In OE or  $\overline{ST}$  mode, a pull-up resistor of 10 k $\Omega$  or less is recommended if pin 1 is not externally driven. If pin 1 needs to be left floating, use the NC option.

- A capacitor of value 0.1 µF or higher between Vdd and GND is required.

# Dynamic Engineers Inc.

2550 Gray Falls Dr., Suite#128, Houston, TX, 77077 TEL: 1-281-870-8822 EMAIL: Sales@DynamicEng.com

# **XO3225AE-37.5MHz-A**High Temperature Oscillator

**Specifications**

| Specifications              |       |                                                                                                                                                               |      |          |       |      |                                |

|-----------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|------|--------------------------------|

| Oscillator                  | Sym   | Condition                                                                                                                                                     |      | Value    |       | Unit | Note                           |

| Specification               | Oy    | Condition                                                                                                                                                     | Min. | Тур.     | Max.  |      | Note                           |

| Frequency Range             |       |                                                                                                                                                               |      | 37.5     |       | MHz  |                                |

| RF Output                   |       |                                                                                                                                                               | l    |          |       | 1    | T                              |

| Waveform:                   |       |                                                                                                                                                               | 0.0= | LVCMOS   |       | .,   | 1011                           |

| Output Voltage Level High   | VOH   |                                                                                                                                                               | 2.97 |          | 0.00  | V    | IOH = -4 mA                    |

| Output Voltage Level Low    | VOL   |                                                                                                                                                               |      |          | 0.33  | V    | IOL = 4 mA                     |

| Output Load Capacitance     |       |                                                                                                                                                               | 45   |          | 15    | pF   |                                |

| Duty Cycle                  |       |                                                                                                                                                               | 45   | 4.0      | 55    | %    |                                |

| Rise/Fall Time              |       |                                                                                                                                                               |      | 1.0      | 2.0   | ns   |                                |

| Power Supply                | \/dd  |                                                                                                                                                               | 2.07 | 2.2      | 2.62  | \ \/ | l                              |

| Supply Voltage              | Vdd   |                                                                                                                                                               | 2.97 | 3.3      | 3.63  | V    |                                |

| Supply Current              | ldd   | OF - Law Output in                                                                                                                                            |      | 3.8      | 4.7   | mA   |                                |

| OE Disable Current          | l_od  | OE = Low, Output in high Z state.                                                                                                                             |      |          | 4.5   | mA   |                                |

| Standby Current             | I_std | ST = Low, Output is<br>weakly pulled down                                                                                                                     |      | 2.6      | 8.5   | uA   |                                |

| Frequency Stability         |       |                                                                                                                                                               |      |          |       |      |                                |

| Frequency Stability         |       | Inclusive of Initial tolerance at 25°C, 1st year aging at 25°C, and variations over operating temperature, rated power supply voltage and load (15 pF ± 10%). |      |          | ±20   | ppm  | In operating temperature range |

| Operating Temperature Range |       | 1070).                                                                                                                                                        |      | -40°C to | 125°C |      |                                |

| Input Characteristics       |       |                                                                                                                                                               |      |          |       |      |                                |

| Input High Voltage          |       | Pin 1, OE or ST                                                                                                                                               | 70%  |          |       | Vdd  |                                |

| Input Low Voltage           |       | Pin 1, OE or ST                                                                                                                                               |      |          | 30%   | Vdd  |                                |

| Input Pull-up Impedence     |       | Pin 1, OE logic high or logic low, or ST logic high                                                                                                           | 50   | 87       | 150   | Kohm |                                |

|                             |       | Pin 1, ST logic low                                                                                                                                           | 2    |          |       | Mohm |                                |

| Startup and Resume Timing   | ı     | <b>16</b> (1                                                                                                                                                  | ı    |          | 1     | 1    | I                              |

| Startup Time                |       | Measured from the time Vdd reaches its rated minimum value                                                                                                    |      |          | 5     | ms   |                                |

| Enable/Disable Time         |       | T_oe = 100 ns + 3 * clock periods                                                                                                                             |      |          | 180   | ns   |                                |

| Resume Time                 |       | Measured from the time ST pin crosses 50% threshold                                                                                                           |      |          | 5     | ms   |                                |

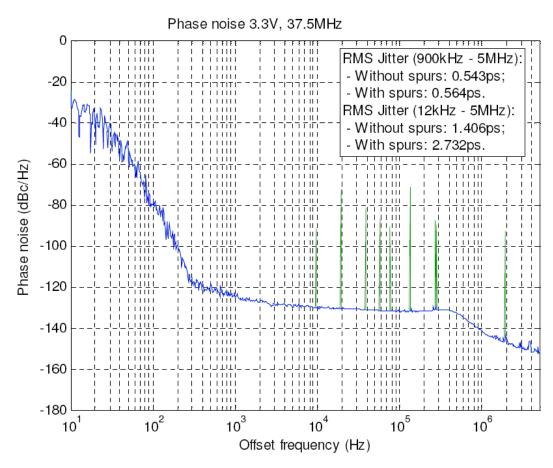

| Jitter PMO Paris de l'itter |       |                                                                                                                                                               |      | 4.0      | 2.5   |      |                                |

| RMS Period Jitter           |       |                                                                                                                                                               |      | 1.6      | 2.5   | ps   |                                |

| Peak-to-peak Period Jitter  |       | Internation to see to 200                                                                                                                                     |      | 12       | 20    | ps   |                                |

| RMS Phase Jitter (random)   |       | Integration bandwidth<br>= 900 kHz to 7.5 MHz                                                                                                                 |      | 0.5      | 0.8   | Ps   |                                |

| (33                         |       | Integration bandwidth<br>= 12 kHz to 20 MHz                                                                                                                   |      | 1.3      | 2.0   | ps   |                                |

# **Absolute Maximum Limits**

| Baramatar                           | Value |      |      | Unit  | Note                                         |  |

|-------------------------------------|-------|------|------|-------|----------------------------------------------|--|

| Parameter                           | Min.  | Тур. | Max. | Ullit | Note                                         |  |

| Storage Temperature                 | -65   |      | +150 | °C    |                                              |  |

| Vdd                                 | -0.5  |      | 4    | V     |                                              |  |

| Electrostatic Discharge             |       |      | 2000 | V     |                                              |  |

| Soldering Temperature               |       |      | 260  | °C    | follow standard Pb free soldering guidelines |  |

| Junction Temperature <sup>[3]</sup> |       |      | 150  | °C    |                                              |  |

Note: 3. Exceeding this temperature for extended period of time may damage the device.

# Thermal Consideration[4]

|   | Package | ΦJA, 4 Layer Board<br>(°C/W) | ΦJA, 2 Layer Board<br>(°C/W) | ΦJC, Bottom<br>(°C/W) |

|---|---------|------------------------------|------------------------------|-----------------------|

| Ī | 3225    | 109                          | 212                          | 27                    |

Note: 4. Refer to JESD51-7 for  $\Phi$ JA and  $\Phi$ JC definitions, and reference layout used to determine the  $\Phi$ JA and  $\Phi$ JC values in the above table.

# Maximum Operating Junction Temperature [5]

| Max Operating Temperature (ambient) | Maximum Operating Junction Temperature |

|-------------------------------------|----------------------------------------|

| 105°C                               | 115°C                                  |

| 125°C                               | 135°C                                  |

Note: 5. Datasheet specifications are not guaranteed if junction temperature exceeds the maximum operating junction temperature.

# **Environmental Compliance**

| Parameter                  | Condition/Test Method     |  |  |  |

|----------------------------|---------------------------|--|--|--|

| Mechanical Shock           | MIL-STD-883F, Method 2002 |  |  |  |

| Mechanical Vibration       | MIL-STD-883F, Method 2007 |  |  |  |

| Temperature Cycle          | JESD22, Method A104       |  |  |  |

| Solderability              | MIL-STD-883F, Method 2003 |  |  |  |

| Moisture Sensitivity Level | MSL1 @ 260°C              |  |  |  |

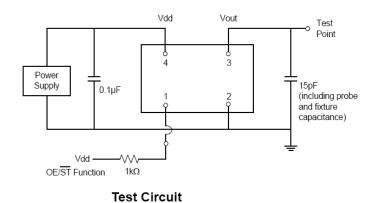

# Test Circuit and Waveform [6]

tr — tf

80% Vdd

50%

20% Vdd

High Pulse

(TH)

Period

Period

Waveform

Note: 6. Duty Cycle is computed as Duty Cycle = TH/Period.

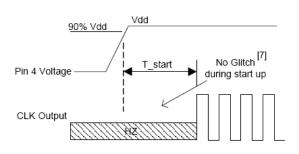

# **Timing Diagrams**

T\_start: Time to start from power-off

# Startup Timing (OE/ST Mode)

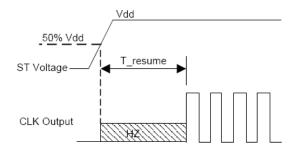

T\_resume: Time to resume from ST

# Standby Resume Timing (ST Mode Only)

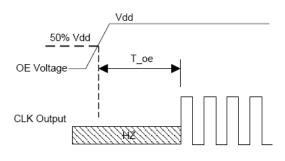

T\_oe: Time to re-enable the clock output

# OE Voltage | 50% Vdd | T\_oe | CLK Output |

T\_oe: Time to put the output in High Z mode

# OE Enable Timing (OE Mode Only)

### OE Disable Timing (OE Mode Only)

Note: 7. XO3225AE has "no runt" pulses and "no glitch" output during startup or resume.

# XO3225AE-37.5MHz-A High Temperature Oscillator

# Pin 1 Configuration Options (OE, ST, or NC)

Pin 1 of the XO3225AE can be factory-programmed to support three modes: Output enable (OE), standby (ST) or No Connect(NC). These modes can also be programmed.

## **Output Enable (OE) Mode**

In the OE mode, applying logic Low to the OE pin only disables the output driver and puts it in Hi-Z mode. The core of the device continues to operate normally. Power consumption is reduced due to the inactivity of the output. When the OE pin is pulled High, the output is typically enabled in <1µs.

### Standby (ST) Mode

In the  $\overline{ST}$  mode, a device enters into the standby mode when Pin 1 pulled Low. All internal circuits of the device are turned off. The current is reduced to a standby current, typically in the range of a few  $\mu A$ . When  $\overline{ST}$  is pulled High, the device goes through the "resume" process, which can take up to 5 ms.

### No Connect (NC) Mode

In the NC mode, the device always operates in its normal mode and output the specified frequency regardless of the logic level on pin 1.

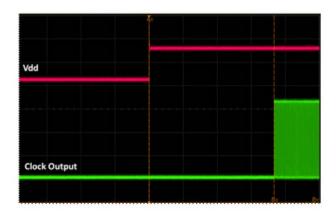

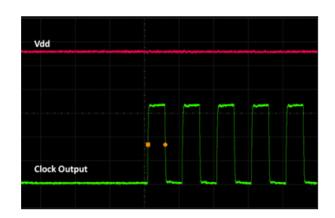

### **Output on Startup and Resume**

The XO3225AE comes with gated output. Its clock output is accurate to the rated frequency stability within the first pulse from initial device startup or resume from the standby mode. In addition, the XO3225AE has NO RUNT, NO GLITCH output during startup or resume as shown in the waveform captures in Figure 17 and Figure 18.

Figure 17. Startup Waveform vs. Vdd

Figure 18. Startup Waveform vs. Vdd (Zoomed-in View of Figure 17)

# **Test Plot**

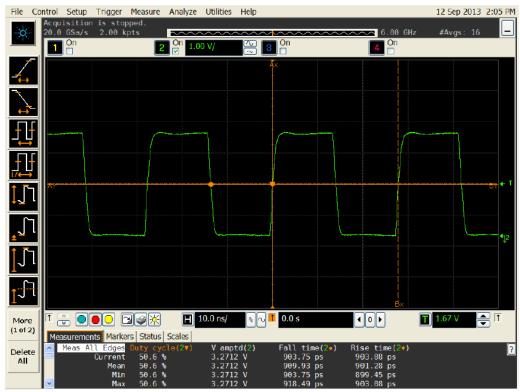

Duty cycle, Rise/Fall time and Amplitude 3.3V

Frequency stability\* versus temperature